FPGA でゲーム機を作ろう(その4)

2019年,最初の記事です。今年もいろんなことにチャレンジしていきたいと思います。

さて,前回は,スクロール BG 画面を作り,画面をスクロールするところまで作りました。

今回は,以下の項目を一気に実装していきます。

- Z80-CPU

- DCSG(SN76489)

- BG の重ねあわせ

- カラーパレット

Z80-CPU

CPU コアは,既存のものを使わせてもらいました。Z80 の IP コアでは比較的有名な「T80」というコアです。

1ChipMSX でも使われていますね。

ユニバーサル基板で手配線した時と同じように,各バスとコントロール信号をHDL 上でデバイスにつなげていきます。

デバイスへのアドレスのデコードは,ロジック IC で作ると,何段かにカスケードして,それぞれのデバイスに接続していくんですが,HDL は,とても簡潔に記述することができて,とても楽です。

また,CPU を動かすことになるので,プログラム用の ROM と RAM も必要です。

これらは,統合環境の Quartus Prime に,FPGA オンチップメモリを使う IP がありますので,それを使い,ROM には,オリジナルの ROM イメージを格納しておきます。

DCSG

音源チップです。

これも,いろいろなコンソールマシンや,アーケードゲームに使われているので,それらでも使用されている既存の IP コアを使わせてもらいました。

そのソースを見るとわかるのですが,矩形波音源は,実は意外と単純な構造になっていることがわかります。

Mr.DO! には,この音源が 2 つ搭載されていますが,これもインスタンスを 2つ記述してそれぞれバスに接続してやります。

BG の重ねあわせ

手配線で作った時は,表示のプライオリティコントロールも実装していました。

CPU からレジスタに値を書き込むことによって,それぞれの BG とスプライトの表示優先順位を変更することができます。

ただ,この Mr.DO! ですが,実は,表示の優先順位は固定されているんです。常に

スプライト > 固定 BG > スクロール BG

となっています。

ですので,今回は,この優先順位変更機能は端折ることにしました。

カラーパレット

オリジナルの基板は,パレットの PROM 出力からフリップフロップを経由して,抵抗とダイオードとトランジスタでアナログに変換して RGB 信号を生成しています。

FPGA ボードの RGB 出力は最終的に抵抗の DAC でアナログ出力していますが,その前段階は,それぞれ 4bit のデジタル信号です。

今回は,PROM のデータからアナログ変換している部分を加味したデータを予めコンバートして生成し,それを PROM の出力とするようにしました。

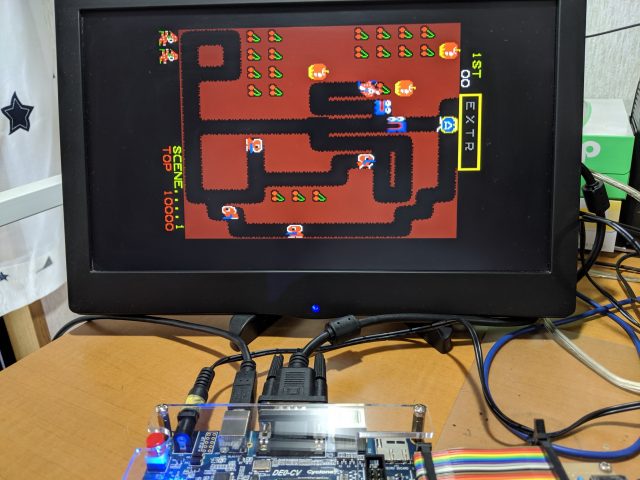

動作確認

以上の項目を実装すると,スプライト表示を除いて,実機と同等の機能になるはずです。

ちょっと音が小さいかもしれません…。

概ね,実機の通りに動いていますが,なぜか,穴を掘ると,掘った通路のキャラが化ける時があります。

原因はまだわかりませんが,こういうのが一番イヤなんですよね…(笑)。

さて,残すはスプライト表示です。キャラ化けの不具合も気になるのですが,まずは,全体の実装を優先して行きたいと思います。