FPGA でゲーム機を作ろう(その5)

すみません…,だいぶ更新をサボっていました。

前回は,スプライトの表示を残して,Mr.DO! が FPGA 上で動作するところまで実装しました。

FPGA でゲーム機を作ろう(その4)

ブログの更新は滞っていましたが,実は,前回から程なくスプライトの実装も完了して,動作確認もできていたのでした。

スプライトの表示

基本的には,スプライトも,ワイヤラッピングで作った時の回路を HDL で書いていくわけですが,元の回路自体がとてもシビアなタイミングで動作しています。

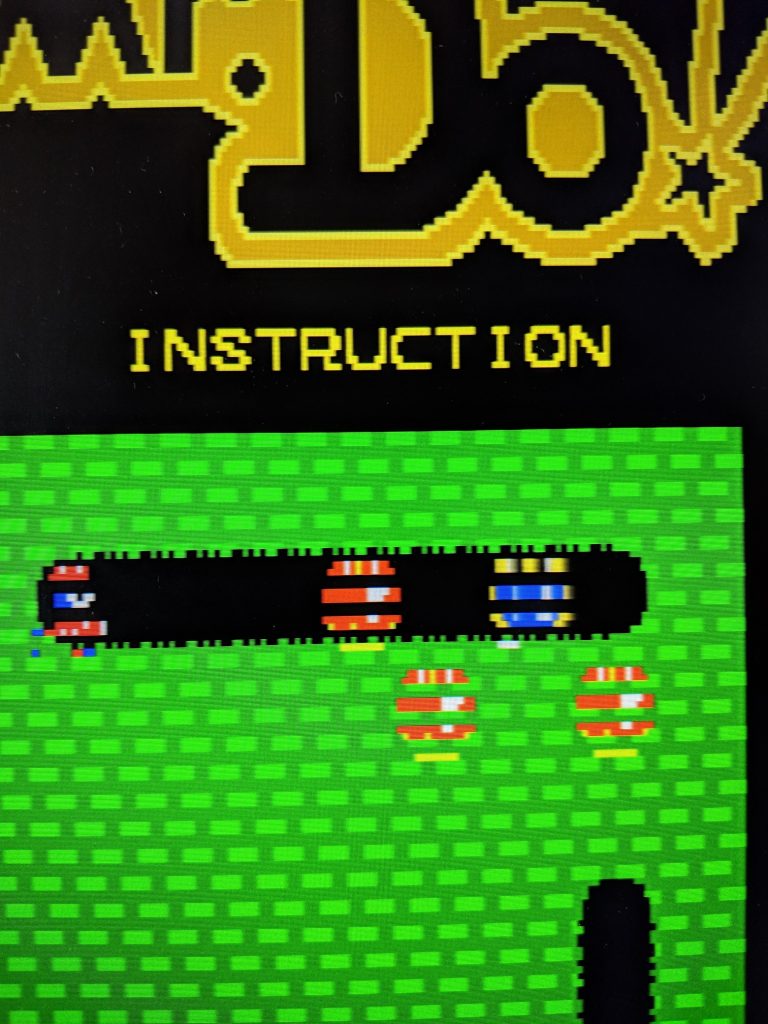

取り敢えず,実装した結果…

「画面に出た!」…と思ったら,縦に2ドットずつ抜けています。

まぁ,表示はされているので,タイミングかな…と思いつつ,ロジックアナライザとにらめっこしましたが,なかなか原因がつかめません。

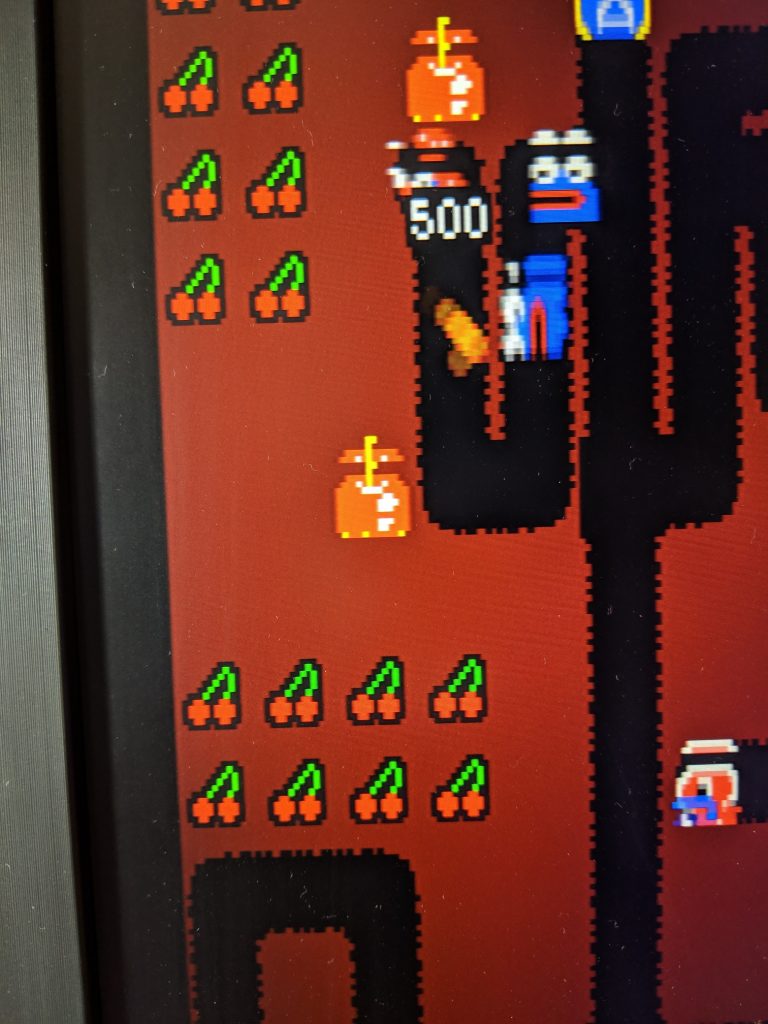

う〜ん,それっぽくなってきましたが,4ドットずれていますね…。

ロジック IC のタイミング

ロジック IC で組んだ元の回路は,信号の遅延を前提とした回路になっています。

いくつかのロジック IC を通して最終的な信号を得る場合,ロジック IC を通るたびに,その出力に時間がかかります。

もちろん,FPGA も遅延はありますが,ロジック IC の比ではありません。

FPGA 側の実装は,基本的にクロック同期設計ですが,場合によっては,オリジナル回路のタイミングを考慮して実装する必要があったりします。

今回の場合は,元の回路をロジック IC で一度組んでいたので,その動作タイミングがある程度理解できていたのですが,たとえ回路図があったとしても,机上のみでその動作を HDL に落とすのは,結構大変だなーと感じました。

BG のキャラ化け

スプライトの表示調整もありますが,前回から,プレイヤーキャラが穴を掘った後の BG が化けて表示されていました。

これもなかなか原因が掴めず,ソフトウェア部分からもアプローチし,プログラムにパッチを当てながら調べたところ,CPU のクロックが足りなかったことが原因だったようです。

CPU へのクロックは,4MHz を入れていたのですが,実は,正しいクロックは,4.096MHz で,若干遅いクロックで動作していたわけです。このクロックの差で,BG への書き込みがうまく行っていなかったようです。

この辺りのタイミングは,ハードウェアエミュレーション独自の問題で,ソフトウェアエミュレータなどでは,CPU をサイクルスチールして画面表示などはしていないので,再現しない問題です。

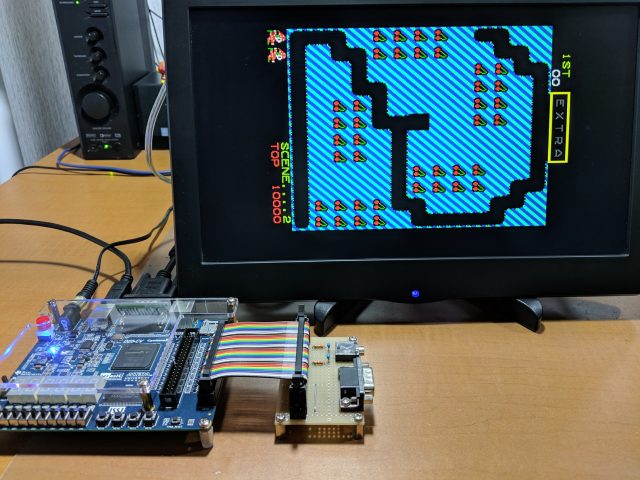

そして完成

スプライト表示と,BG の不具合を修正し,オリジナル基板と同等の動作をするようになりました。(ワイヤラッピングの時と同様,テーブル筐体で二人プレイした時の画面反転は実装していません)

…ということで,FPGA での Mr.DO! はこれで完成とします。

次回は…,う〜ん,最近はあまり時間が取れないのですが,何か自分仕様のゲーム機回路でも作ってみようかな〜と思います。