FPGA でゲーム機を作ろう(その3)

今年ももう年末です。いろいろとやらなくてはいけないことがあって,時間が取れないのですが,少しずつ進めていきます。

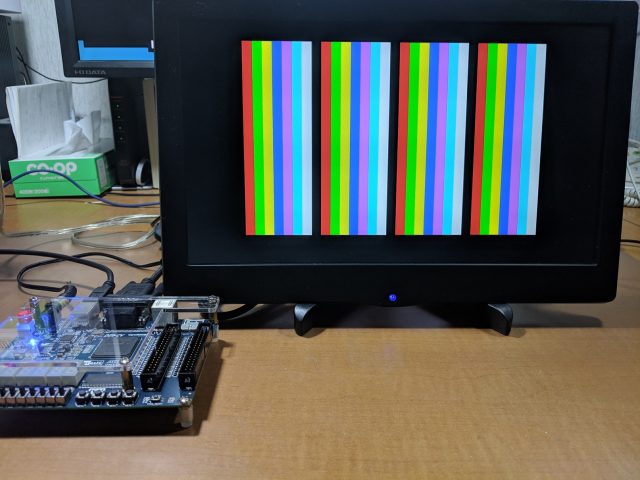

前回は,画面表示制御信号を生成し,モニターに表示するところまで作りました。

今回は,BG 画面の出力部分を作ります。

基本は,回路をそのまま HDL に落とします

BG 画面の表示の仕組みは以前の記事をご覧ください。

基本的には,以前作った回路をほぼそのまま HDL で書き直します。

水平カウンタと垂直カウンタから VRAM のアドレスを生成し,VRAM から読みだしたデータからさらに,CGROM のアドレスを生成します。

そして,CGROM から読みだしたデータを 1bit ずつモニターに出力してやればBG 画面が表示できます。

回路の使い回し

ロジック IC で作った時は,2 面ある BG は,物理的に 2 つ分の回路として基板を作りました。

ほぼ同じ回路を 2 つ作る必要があったわけです。

HDL で書く場合は,当然,似たような回路は使い回しができます。

ソフトウェアで言うところの,クラスとインスタンスのような感じです。

Mr.DO! には,固定 BG と,スクロール BG がありますが,その違いは表示開始位置を指定するスクロールレジスタがあるかないかです。

固定 BG は,スクロールレジスタをゼロ固定にしても表現することができるので,今回は,スクロール BG を 2 つ実装して,片方はスクロールレジスタの値を固定するようにしました。

スクロール BG の表示

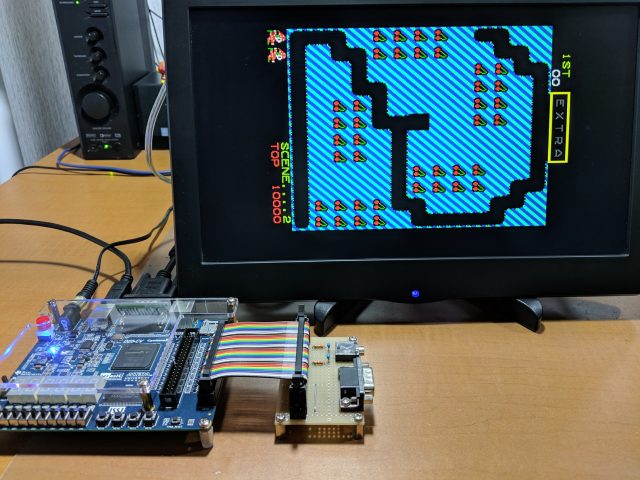

まだ,画面の重ねあわせができないので,スクロール BG のみを表示してみます。

CPU も接続していないので,とりあえず,垂直カウンタをスクロールレジスタに接続して,縦横スクロールするようにしています。

さて,次回は,Z80 の IP コアを接続してみたいと思いますが,今年も残りあと僅かですので,次回は年明けになりそうですね。

それでは,良いお年を!