オレ仕様のゲーム機を作ろう(その15)

前回は,画面背景を表示する「ビデオボードその1」を作りました。

オレ仕様のゲーム機を作ろう(その14)

今回は,最後の基板「ビデオボードその2」を作っていきます。

これで,今回の「オレ仕様ゲーム機」は完成となる予定です。

スプライト表示

前回で,複数枚の BG 画面を作りましたので,残っているスプライト表示部分を作ります。

過去に似たような回路を作っているのですが,なぜか毎回うまく表示されない鬼門でもあります。

ユニバーサル基板で作った「オレ仕様ゲーム機」では,以下のような機能を持っていました。

- 画面中に 128 枚同時表示

- 同一水平ライン上に 16 枚まで表示可能

- 1 枚につき単色表示

さて,今回どのくらい機能アップするかと言うと…

- 画面中に 128 枚同時表示

- 同一水平ライン上に 32 枚まで表示可能

- 1 枚につき 4 色表示

同時表示枚数は,変わらず 128 枚までです。

色数は,4 色表示(うち透明色がありますので,実質 3 色)に増やしましたが,部品を増やせば,16 色表示も可能です(これは次回に持ち越しします)。

同一水平ラインに表示できる枚数は,16 枚から 32 枚まで増やしますが,ここが今回一番不安な部分です。

基本的な動作原理は,以前の基板とさほど変わりませんので,説明は省略します。

スプライト横並び枚数の増加

FPGA のような,数十メガヘルツでも動作可能(もちろん対応するメモリも)な場合は,スプライトをレンダリングするクロックを上げてやれば,横並びの枚数を増やすことができます。

今回は,74 ロジックを使った回路です。

一つ一つの IC は,入力信号をごにょごにょと処理をして出力信号を出しますが,この時に,ある程度の遅延時間が発生します。

この遅延時間は,電圧や温度によって多少変化しますが,数ナノ秒から十数ナノ秒掛かるので(IC の種類にもよる),複数の IC を繋げたりすると,最終結果が出るまでに数十ナノ秒掛かったりするんですね。

74AC タイプの IC を使うと,多少この遅延時間を短縮することができますが,できれば,なるべく入手しやすい 74HC タイプを使いたいところです。

こうなると,1 枚のスプライトを処理するのにかかる時間から,どうしてもラインバッファにレンダリングできる枚数が限られてしまいます。(少なくとも今の自分の技術力では)

方法はいくつかあると思いますが,今回は,複数のドット(ピクセル)を同時にレンダリングすることで,この辺りの時間を稼ぐことにしました。

BG との表示優先順位

さて,最終的にディスプレイモニターに出力するには,前回作成した BG 基板から出力される信号とミックスして出力してやる必要があります。

このミックスする際に,それぞれ自由に表示優先順位を変更できるようにしたかったのですが,そのための回路も必要になるので,今回は省略して,表示優先順位は固定としました。

2 つの BG の間にスプライトが挟まるようにしました。

この程度のスペックのゲーム機なら,これでも大丈夫だと思います。

パレットでの色変換

最近のゲーム機は,あまり「パレット機能」と言う言葉も聞かなくなったような気がします。

今回のゲーム機は,BG,スプライトともに,1 ドット当たり 4 色表現できます(うち,1 色は透明色)。

この 4 色の組み合わせを,パレットに 16 種類定義でき,その中から 1 種類を BG のパターンと,スプライト 1 枚に,それぞれ割り当てることができます。

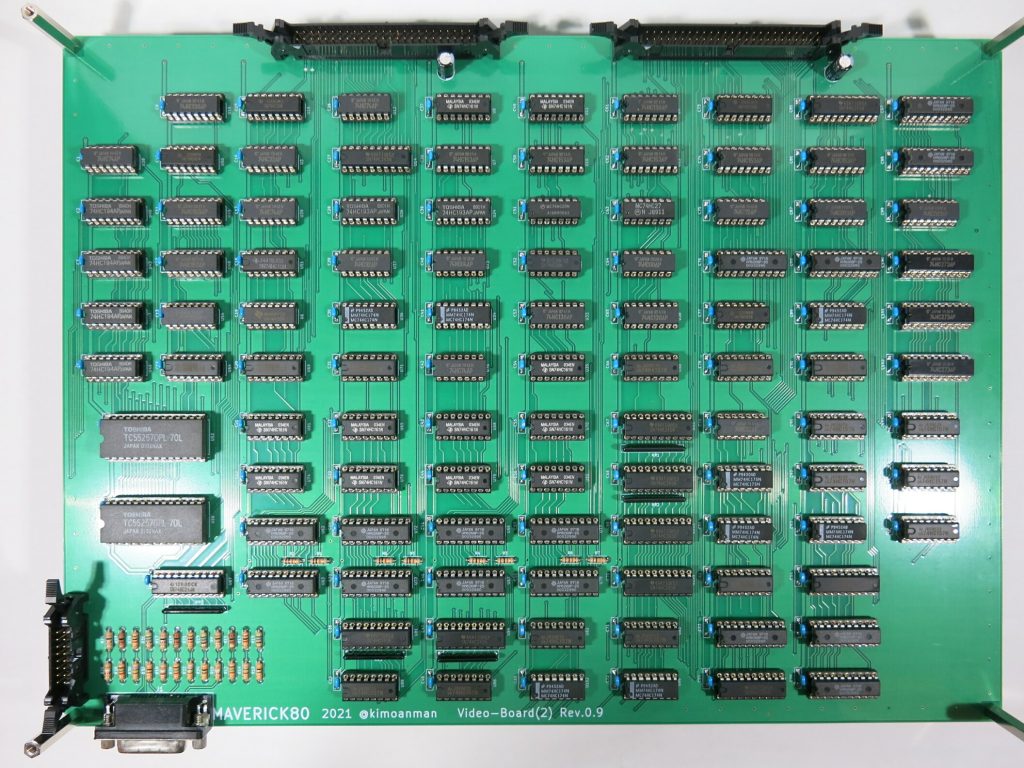

作成した基板

こちらが,作成した スプライト基板です(クリックで拡大します)

IC やメモリの配置がうまくいかず,配線が結構大変でしたが,縦横きれいに並べることができました。

手持ちの高速 SRAM が,データバス 4bit のタイプしかなかったので,SRAM の使用個数が多くなってしまいました。

やっぱり一発では動かない

今回もこのパターンです(笑)。

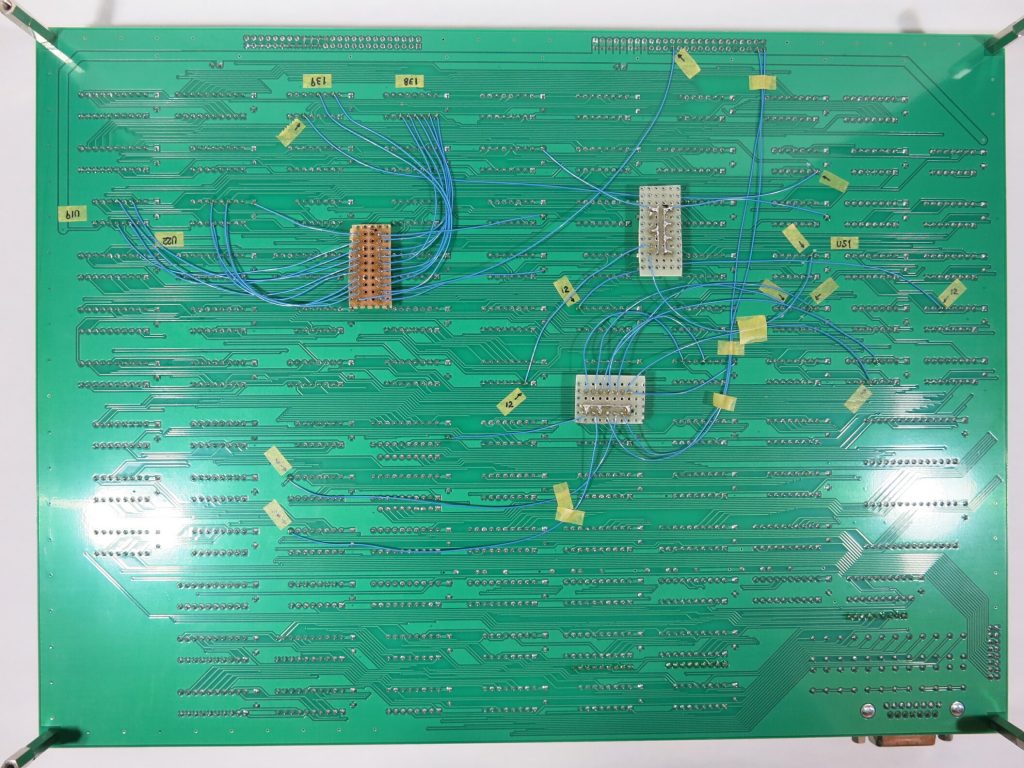

基板裏側で修正した結果がこちらです。

今回もひどいですね。

修正点としては…

8bit のカウンタを D-FF で補足するのを忘れていたので,左側にゲジゲジみたいなものが追加されています。

ラインバッファへの書き込みタイミングが,クロック立ち下がりで行わなければならないところを,立ち上がりで行っていたので,右上にインバータを追加しています。

ラインバッファへのアクセス時のチップセレクト制御が間違っていて,データバスがぶつかっていたのと,クロック信号のバッファリングで,真ん中に ORゲートを追加しました。

回路が複雑なので,不具合を特定するのがとても大変で,意図通りに表示できるまで,結構時間がかかってしまいましたが,根気よく対応して,なんとか動作させることができました。

そして完成

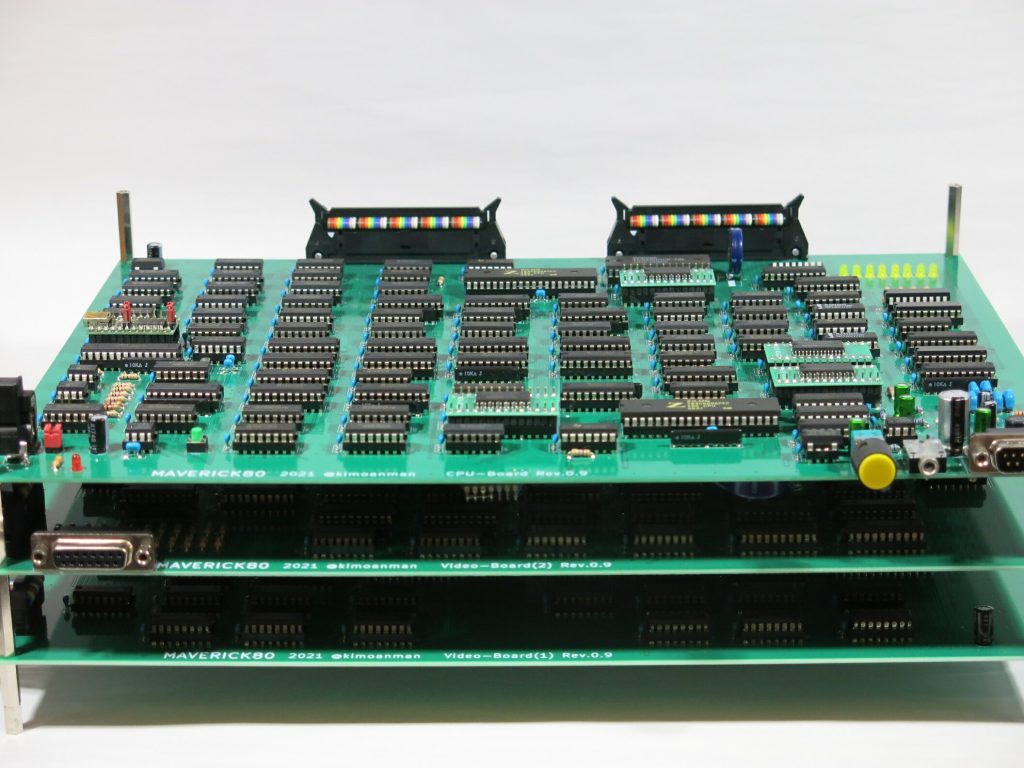

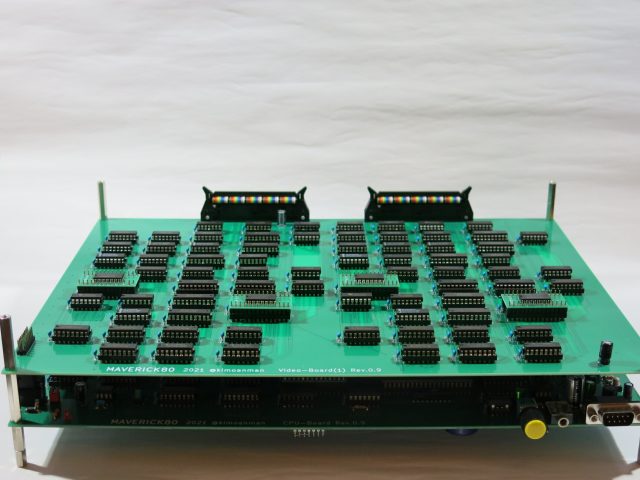

「CPU ボード」と「ビデオボードその1」と接続してみます。

最終的に,この基板の大きさで 3 階建てになりました。

基板が 3 枚で,DIP の部品(74 ロジック,Z80,メモリ,音源…)が全部で282 個です。

基板製造費,部品代,諸々で 6 万円くらい掛かってしまいました。

FPGA の評価ボードが 3 つくらい買えるかもしれませんね…(笑)。

動作確認

さて,これまでお馴染みのテストプログラムを実行させてみます。

メイン CPU,サブ CPU ともに,プログラムは SRAM をバックアップしていますので,電源オンで起動します。

(音量注意!)

途中,かなりピンぼけしてますね…。

最初の回路図の日付が,2021年5月6日になっているので,約半年近くかかりましたが,なんとか完成することができました。

このブログ記事は,割と最近更新していますが,実は,基板自体は,かなり前から動かしていました。

今回は,もしかしたら意図通り動かないかもしれない…,完成まで漕ぎ着けることができないかもしれない…と弱気になっていたので,ある程度,完成が予測できる段階まで,ブログに紹介できずにいたのでした…(オイ)。

最初のうちから「いついつ完成予定〜」と言っておいて,途中「忙しくて遅れています」となり,そのうち「…無言」となる可能性も十分あったわけです。(いわゆるヤルヤル詐欺?)

さて,これで「オレ仕様のゲーム機」もゲーム機らしくなってきましたが,「オレの理想の Z80 ゲーム機」は,もう少しやりたいことがあります。

段階的に機能アップしてきて,ノウハウも蓄積されて来ましたが,「オレ仕様のゲーム機」作成はまだまだ続く予定です(いつとは言わないw)。

さて,次回ですが,今回のテストプログラムが比較的簡易的なものだったので,もう少しテストプログラムを拡張していきたいな…と思っています。

それでは,次回に続きます。